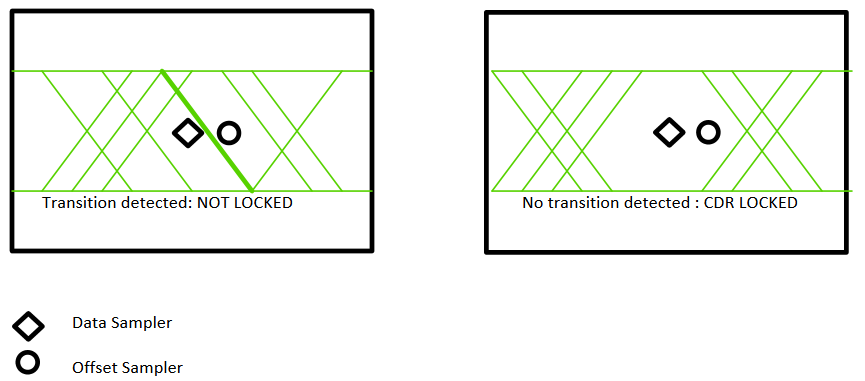

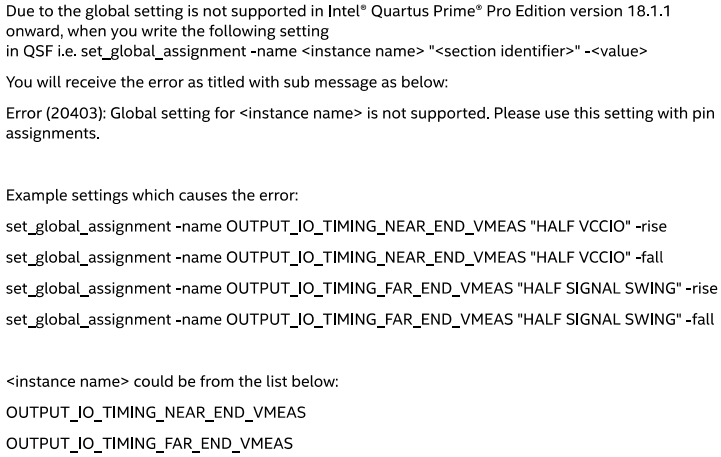

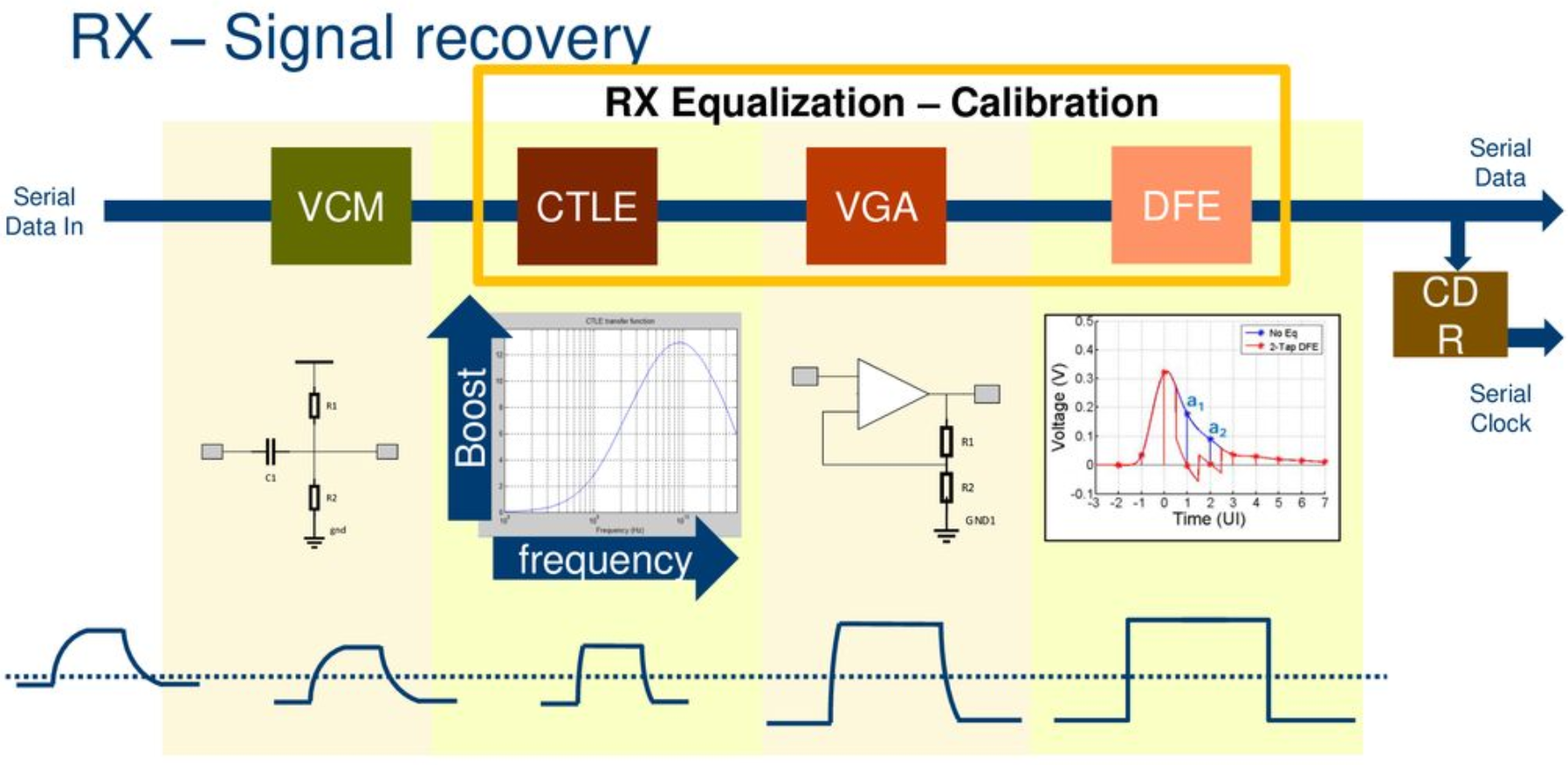

Xilinx Tranceiver 에서 CDR이 수신 데이터가 locked 되어 있는지 확인하는 방법설명Clock and Data Recovery 장치(CDR)는 직렬 수신기의 핵심입니다.수신 직렬 데이터에서 병렬 도메인(복구된 데이터 및 복구된 클록과 동일한 위상)으로 변환할 수 있습니다.CDR은 데이터 전환을 지속적으로 측정하여 복구된 클록의 위상을 제어합니다.모든 구성 및 신호 요구 사항이 충족되면 CDR은 locked 조건으로 수렴할 수 있습니다.그러나 이 조건이 충족되었음을 나타내는 신호는 없습니다.복구된 데이터는 언제 신뢰할 수 있는 것으로 간주될 수 있습니까?----------------------------------------------------------------------------..