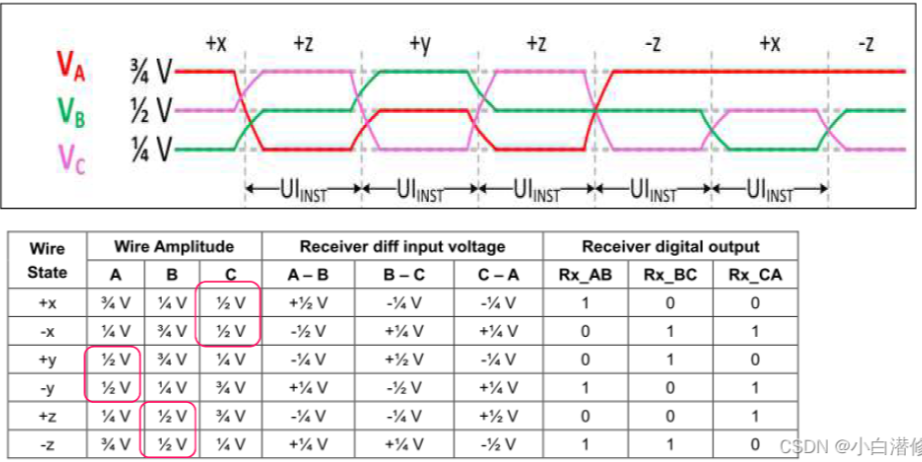

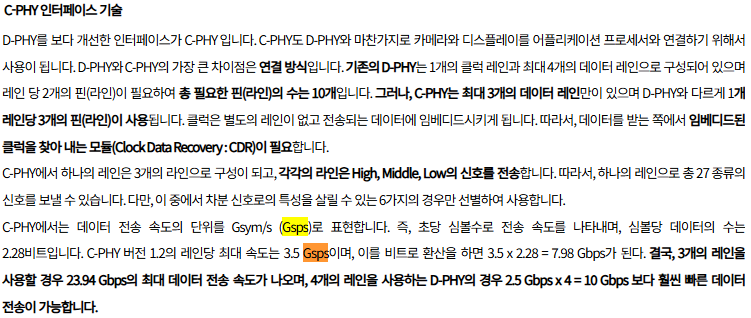

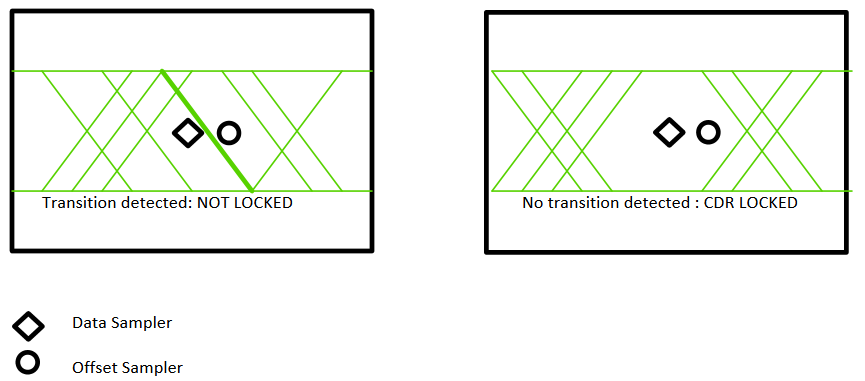

CPHY PDAF 모드란?CPHY PDAF(Phase Detection Autofocus) 모드는 카메라 센서의 CPHY(C-PHY) 인터페이스와 위상 검출 자동 초점(PDAF, Phase Detection Autofocus) 기술을 결합한 방식입니다.1. CPHY란?CPHY는 MIPI(CSI-2) 표준을 기반으로 한 고속 데이터 전송 방식으로, 기존의 DPHY(D-PHY) 방식보다 효율적인 데이터 전송이 가능합니다.DPHY vs. CPHY 비교DPHY: 병렬 데이터 전송 (1개 라인당 2개의 전송 채널)CPHY: 3개 신호선을 활용한 차등 신호 방식으로 더 높은 대역폭과 저전력 소모 가능2. PDAF란?PDAF는 이미지 센서에서 위상 차이를 이용해 초점을 빠르게 맞추는 자동 초점(AutoFocus) 기..