Xilinx Tranceiver 에서 CDR이 수신 데이터가 locked 되어 있는지 확인하는 방법

설명

Clock and Data Recovery 장치(CDR)는 직렬 수신기의 핵심입니다.

수신 직렬 데이터에서 병렬 도메인(복구된 데이터 및 복구된 클록과 동일한 위상)으로 변환할 수 있습니다.

CDR은 데이터 전환을 지속적으로 측정하여 복구된 클록의 위상을 제어합니다.

모든 구성 및 신호 요구 사항이 충족되면 CDR은 locked 조건으로 수렴할 수 있습니다.

그러나 이 조건이 충족되었음을 나타내는 신호는 없습니다.

복구된 데이터는 언제 신뢰할 수 있는 것으로 간주될 수 있습니까?

-------------------------------------------------------------------------------------------------------------------------------------------------------------

솔루션

역사적으로 올바른 수신 데이터는 CDR이 잠겨 있음을 이해하는 유일한 확실한 방법이었습니다.

대부분의 데이터 인코딩 체계는 수신기 측에서 오류 감지를 허용하며 이는 locked된 CDR에 대한 플래그로 광범위하게 사용되었습니다.

그러나 이 방법은 항상 적용되는 것은 아니며 사용자는 데이터가 양호할 때 CDR에서 알고 싶어할 수 있으며 그 반대는 아닙니다.

"locked" 조건을 결정하는 또 다른 시험적인 방법은 CDR loop의 제어 신호를 조사하는 것입니다. "locked" 상태에서 이 제어 신호는 작은 변화가 있을 것으로 예상됩니다.

이 측정은 많은 거짓 양성 또는 불안정한 조건을 피할 수 없으며 일반적으로 지원되지 않습니다.

사용 가능한 경우 RXCDRLOCK 신호는 "reserved"으로 표시됩니다.

데이터 샘플러와 오프셋 샘플러 간의 실시간 비교는 참되고 일반적인 CDR LOCK 결정을 위한 실행 가능한 솔루션 중 하나입니다.

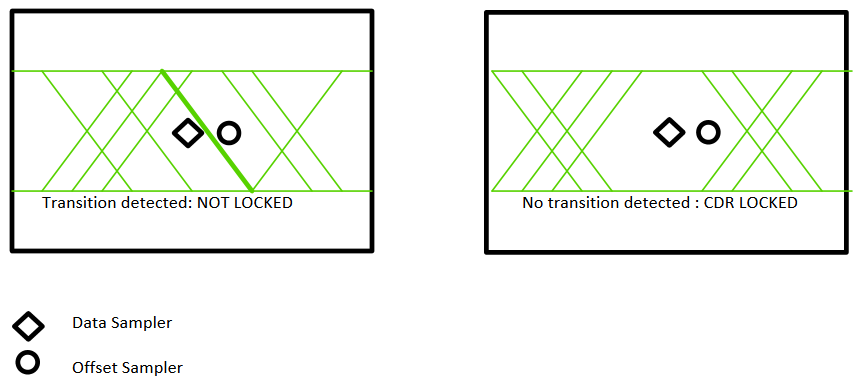

CDR이 데이터에 locked 되면 트랜시버는 전환에서 멀리 떨어진 데이터를 샘플링합니다.

반대로 CDR이 아직 locked 되지 않은 경우 데이터 전환은 모든 위치에서 아이 윈도우를 교차할 수 있습니다.

데이터 샘플러와 오프셋 샘플러가 항상 동일한 정보를 수신하는 경우 데이터 샘플러와 오프셋 샘플러 간에 전환이 교차하지 않는다는 것을 의미합니다.

수직 오프셋 = 0과 수평 오프셋을 몇 단계(예상 눈 너비보다 훨씬 작음)로 설정하면 오프셋 데이터 오류의 연속 측정을 통해 데이터 샘플러와 오프셋 샘플러 간에 발생하는 모든 전환을 알 수 있습니다.

이 측정을 통해 CDR이 스위핑되지 않는다는 것을 확인할 수 있습니다.

참조 : https://support.xilinx.com/s/article/66699?language=en_US

66699 - how to check that the CDR is locked to incoming data

The Clock and Data Recovery unit (CDR) is the heart of the serial receiver. It allows the conversion from incoming serial data to the parallel domain (in recovered data and in phase with the recovered clock). The CDR controls the phase of the recovered c

support.xilinx.com

'[FPGA]' 카테고리의 다른 글

| CRA [Chief Ray Angle] 이란? (0) | 2024.02.13 |

|---|---|

| modelsim :: Error: (vlog-13069) : near "EOF": syntax error, unexpected end of source code. 해결 방법 (0) | 2022.11.05 |

| [IntelFPGA] Quartus compile 중 "Sorry!" error 발생 대응 방법 (actl_root.cpp) (0) | 2022.09.28 |

| Error (329006): Some pins have illegal board trace modelsDescription (0) | 2022.07.19 |

| MGT(Multi-Gigabit Transceiver) PCS, PMA (0) | 2021.10.29 |