TSE는 아래와 두가지로 port가 나누어져 있습니다.

Control을 위한 avalon MM slave port

Data를 위한 Avalon Streaming port

(참고적으로 Avalon Streaming sink는 input이구요..

Avalon Streaming Source는 output이죠)

필요한 Component는 총 4개 입니다.

1. TSE component

2. TX SG-DMA

3. RX SG-DMA

4. SG-DMA descriptor memory

자 이것을 바탕으로 SOPC Builder에서 TSE를 한번 붙여보죠..

1. TSE Component

먼저 TSE를 선택해서 simple하게 10/100만 지원하는 MAC을 만들어 보죠..

이놈을 double click하면 됩니다.

이놈을 double click하면 됩니다.

그럼 아래와 같은 화면이 나타나는 데요..

여기서 Core Variation을 "10/100Mb Small MAC"으로 설정합니다. 그럼 자연적으로 interface는

MII가 됩니다.

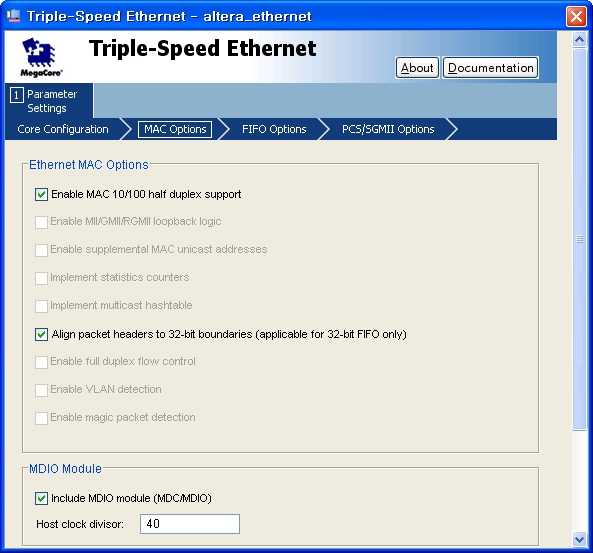

다음으로 옵션에서

위와 같이 기본설정을 하구요,, 외부 external PHY chip access를 위한 MDIO module를 활성화 합니다.

MDIO는 serial통신 protocol로써(I2C와 비슷) 일반적으로 clock은 2.5MHz정도면 충분합니다.

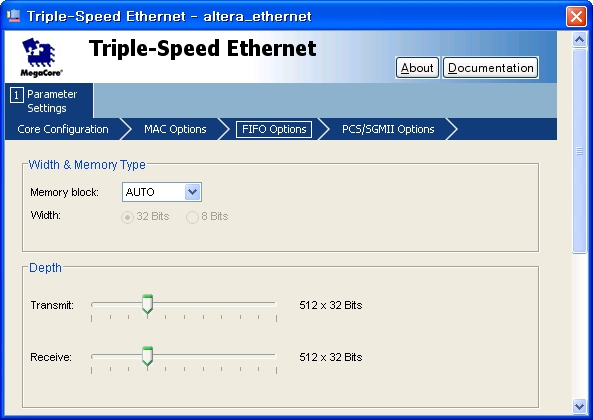

마지막으로 tx/rx fifo을 설정해 보죠.

저기는 저는 아주 simple하게 fifo의 크기를 2048씩만 잡았습니다.

이 FIFO의 크기에 의해서 Ethernet MAC의 Throughput이 결정됩니다.

여기까지 하고 Finish..

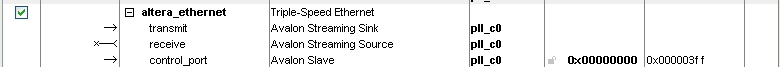

그럼 아래와 같이 component가 만들어 진것을 보실수 있습니다.

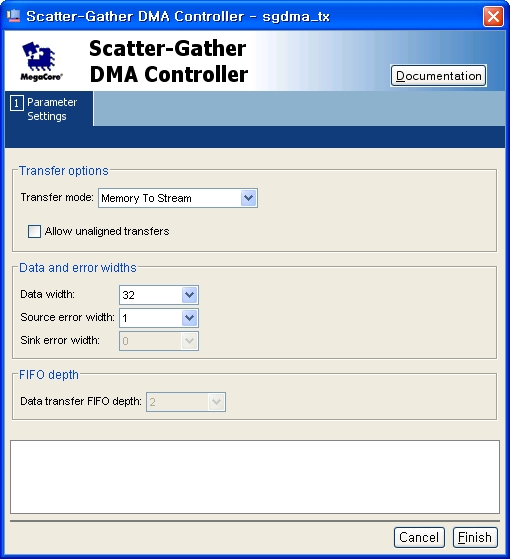

2. TX SG-DMA

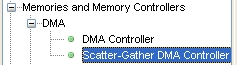

SG-DMA는 아래와 같은 곳에 숨어 있으므로 찾아서 쓰시면 됩니다.

TX는 TSE에 데이타를 write화는 것입니다. 그럼 external PHY를 통해서 외부로 나가겠죠.

그렇게 볼때 TSE Streamming이므로 TX를 위한 SG-DMA는 memory to stream이 당연히 되겠죠..

아래와 같이 설정을 하시면 되겠습니다.

3. RX SG-DMA

tx와는 반대로 RX SG-DMA는 외부에서 ethernet packet이 들어와서 TSE의 rx fifo에 저장된것을

읽어와는 입장이걸랑요..

그래서 당근 Stream(TSE) to Memory(rx buffer working memory)가 되겠죠..

위와 같이 설정을 하면 되겠습니다.

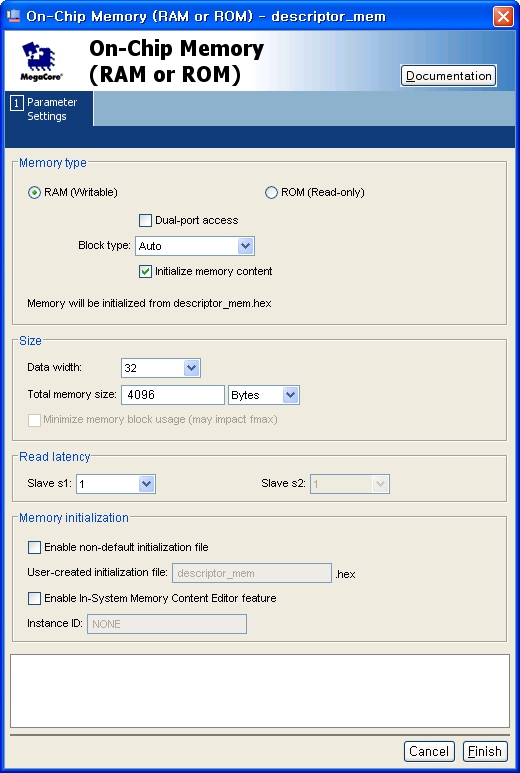

4. SG-DMA을 위한 descriptoer memory

SG-DMA를 위해서 아래와 같이 descriptor memory를 4K정도 잡습니다.

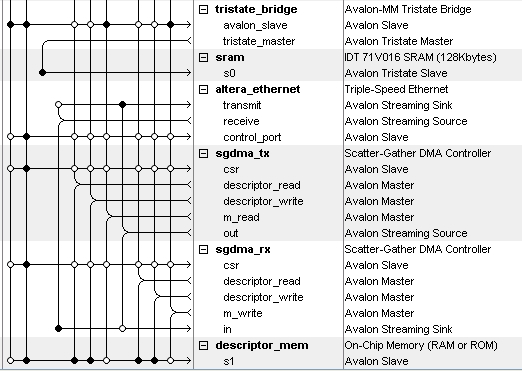

자 여기까지 하면 아래와 같이 4개의 component가 다 만들어 졌네요..

Connection

이제 이해를 하면 쉽지만 이해못하면 항상 어려운 만들어진 component끼리의 연결이 남았습니다.

여기서 일단 머리에 알아 두어야할 사항이..

TSE의 transmit은 input이고, receive는 output이다..

이것만 일단 기억하구요.. 연결을 해보죠..

TX-SG DMA (Memory to Stream)

일단 sgdma의 descriptor read / wirte는 descriptor memory에 연결합니다.

이놈의 읽은 저희가 Memory to Stream으로 만들었으니까..

memory에서 어떤 값을 read어서 : 이것이 m_read port <-- 어디서 working memory

Stream에다가 그 값을 써주면 : 이것이 out port --> 어디에다가 TSE의 transmit port

가 되겠습니다.

따라서 m_read는 TSE로 보낼 packet이 준비되어있는 working memory를 지정하면 되겠구요.(여기서는 sram)

out은 TSE의 transmit에 연결을 하면 되겠습니다.

RX-SG DMA (Steram to Memory)

Tx와 반대죠.. 하여간 이놈의 descriptor read / wirte도 descriptor memory에 연결합니다.

그리고 이놈의 하는 일을 보면

Stream에서 어떤 값을 읽어다가 : 이것이 in port <-- 어디에서 읽어올까 TSE의 receive

memory에다가 쓰면 된다. : 이것이 m_write port --> 어디에다가 working memory

따라서 m_write는 working memory에 in은 TSE의 receive에 연결합니다.

그래고 TSE의 control port, SG-DMA의 CSR들은 모두 Nios II의 data master와 연결을 하면 되는 것이지요..

여기까지 하고 나면 아래와 같은 결과를 보실수 있습니다.

자 이렇게 하면 되는것이죠..

마지막으로 IRQ number를 적정히 주시구요.. auto_assing base address를 하면 끝나는 것입니다.

음.. 여기까지 하고.. 다음에.. Quartus II에서 External PHY와 연결하는 것을 설명하도록 하겠습니다.

'[FPGA]' 카테고리의 다른 글

| genver 사용 방법 (0) | 2015.11.19 |

|---|---|

| [altera] Error: {variation_name}_p0_pin_map.tcl: Failed to find PLL reference clock (0) | 2015.11.16 |

| Quartus에서 Tri-Speed Ethernet MAC(TSE)붙이기-2 (0) | 2015.07.01 |

| FPGA sof(or pof) image에서 onchip memory 내용만 간단히 update하기 (0) | 2015.07.01 |

| [Altera] spread spectrum clocking (0) | 2015.05.22 |