자.. 이제 SOPC Builder에서 만들어진 TSE를 Quartus에서 붙이는 것을 한번 보겠습니다.

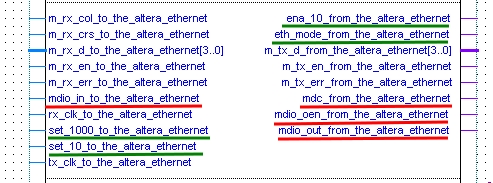

만들고 보면 위와 같은 보이실 겁니다..

위에서 보면 빨간색 밑줄이 그어져 있는 부분이 MDC/MDIO에 대한 부분이구요.

녹색 밑줄이 option이고, 나머지는 External PHY chip과 연결이 된다고 보면 되겠습니다.

왼쪽은 input이구요, 오른쪽은 output이 되는 것입니다.

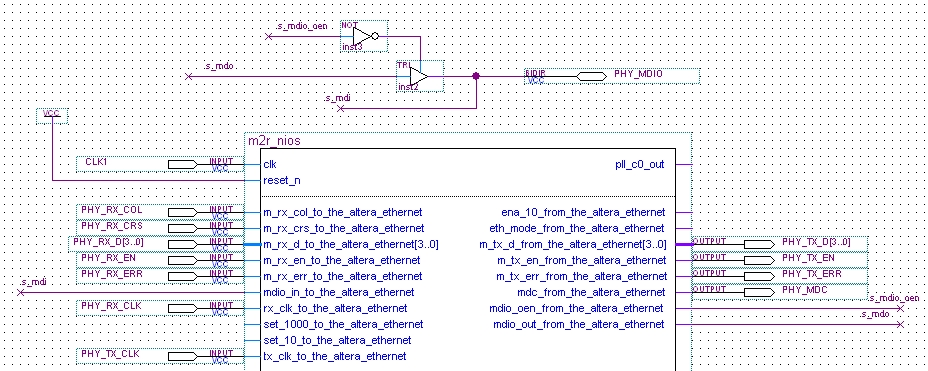

PHY chip과 연결

External PHY chip과 아래와 같은 신호들이 연결됩니다.

PHY TSE

tx_clk, rx_clk ----> m_tx_clk, m_rx_clk (_to_the altera_ethernet은생략)

rx_col, rx_crs ----> m_rx_col, m_rx_crs

rx_d[3..0] ----> m_rx_d[3..0]

rx_en, rx_err ----> m_rx_en, rx_err

tx_d[3..0] <---- m_tx_d[3..0]

tx_en,tx_err <---- m_tx_en, m_tx_err

다음으로 PHY chip의 MDC/MDIO 연결

PHY TSE

mdc <---- m_mdc

mdio <----> mdio_out, mdio_in

여기서 mido pin은 bidirection으로 아래와 같이 TSE에서 나오는 mdio_oen 신호를 이용해서

mdio_out과 mdio_in으로 연결을 해줘야 합니다. (vhdl coding, tri-state buffer를 하나 달아주는 것이죠..)

mdio_in_to_the_tse_mac <= mdio;

mdio <= mdio_out_from_the_tse_mac when mdio_oen_from_the_tse_mac = '0' else 'Z';

이렇게 하고.. option pin들의 input들은 모두 GND로 하고 output들은 모두 open시켜놓으면

연결이 끝나는 것이죠..

이렇게 붙여주면 되는것이죠..

이렇게 한 다음에는 TSE의 test는 Nios II IDE에서 simple socket server같은 하나 실행시켜 보면..

잘 될겁니다.

Nios II IDE software에 관한 것은 다음에..

'[FPGA]' 카테고리의 다른 글

| [altera] Error: {variation_name}_p0_pin_map.tcl: Failed to find PLL reference clock (0) | 2015.11.16 |

|---|---|

| Quartus에서 Tri-Speed Ethernet MAC(TSE)붙이기-1 (0) | 2015.07.01 |

| FPGA sof(or pof) image에서 onchip memory 내용만 간단히 update하기 (0) | 2015.07.01 |

| [Altera] spread spectrum clocking (0) | 2015.05.22 |

| [Altera] timing simulation 방법 (0) | 2015.03.05 |