이미지 센서는 wafer 공정회사 또는 반도체 회사 에서 제조된다. 여기에 있는 조그만한 회로와 장치들은 실리콘 칩 위에 새겨진것이다. CCD의 가장 큰 문제는 더 이상 경제적인 스케일이 충분치 않다는 점이다. CCD가 만들어지기 위해서는 전문적이고 값비싼 공정을 통해야 한다.

반면, 보다 많은 반도체 공장들은 몇백만의 컴퓨터 프로세서와 메모리 칩을 만들기 위해 Complementary Metal Oxide Semiconductor (CMOS)라고 불리는, CCD와 전혀 다른 방법을 사용하고 있다. 이 방식은 현재까지 세계에서 가장 일반적이면서도 높은 생산 방식이다.

| CMOS image sensor의 역사 CMOS Image Sensor(CIS : Contact Image Sensor라고도 함)는 1967년 FairChild, RCA등이 활발히 개발을 하기 시작하였다. 그 후, 1979년 Hitachi가 개발에 주력을 하다 Fixed Pattern Noise (FPN)를 비롯한 각종 noise로 인하여 image quality가 CCD에 비해 열등해지고 회로의 복잡성에 의해 Packing Density가 낮아졌다. 또한 비용면에서도 CCD에 비해 그다지 차이점이 없었을뿐만 아니라, chip size가 큰 이유로 1989년, MOS형 센서의 개발을 포기하고 CCD 개발으로의 전환을 꾀하였다. 이후 1990년 NHK/Olympus에서 amplified MOS Imager (AMI)를 발표하였고, 1993년 edinburgh 대학에서 최초의 CMOS type Camera chip을 발표한 이후로 같은해 JPL에서 CMOS type Active Pixel Sensor(APS)를 발표하고 1995년 미국 대학 및 연구기관에서 본격적인 CMOS Image Sensor에 대한 개발이 시작되었다. |

CMOS image sensor의 Pixel구조 및 동작원리

1-Tr Structure

1 Tr Structure의 경우 그림과 같이 아주 간단한 구조로 구성된다.

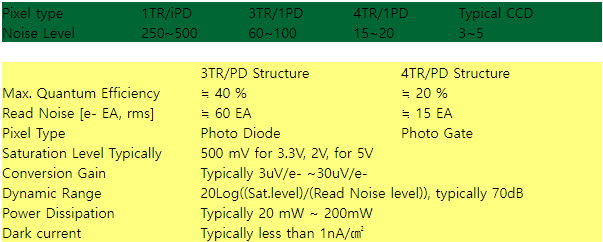

1 pixel을 구성하는 요소가 MOSFET 1ea, PhotoDiode 1ea로 구성되므로 동일한 pixel size에 대해서 2 ~ 4TR 구조의 pixel 보다 수광부 면적을 크게 할 수 있는 장점이 있다. 또한 70 ~ 80 %에 이르는 fill factor를 얻을 수 있다. 그러나 signal readout시 noise level이 대략 250 e- [r.m.s] 정도로 매우 크게 나타나며, signal 증폭용 sense amp(S/A) 및 signal 저장용 capacitance가 bus line 끝단에 존재하므로 parastic capacitance의 영향을 많이 받아 결과적으로 Fixed Pattern Noise(FPN)가 크게 나타나는 단점이 있다.

이러한 구조로는 photo-diode type passive pixel구조와 Charge Modulation Device(CMD)가 있다. 그러나 CMD의 경우 standard CMOS process를 사용하지 않고 특별한 process를 적용하기 때문에 non-CMOS active pixel sensor(APS)라고 불리기도 한다.

1 Tr구조의 동작은 수광부에 빛이 입사하게 되면 이에 따라 EHP(Electron-Hole Pair)가 생성되고, 이렇게 생성된 신호전하는 Tr의 gate bias에 따라 출력단으로 전달되는 방식으로 되어 있다.

3-Tr Structure

1 Tr 구조가 가지고 있는 parastic capacitance에 의한 noise를 제거하기 위하여 1968년에 일본의 Noble이 제안한 구조로써 1980년대 후반에 NHK에서 개발한 구조이다.Pixel 내에 source follower를 삽입한 구조로써 photo-diode type active pixel sensor(APS)라고 부르기도 한다.

1 pixel내에 3개의 Tr과 1개의 photo-diode가 첨가되어 있으므로 1 Tr 구조에 비해 상대적으로 fill factor가 낮으며, parastic capacitance에 의한 noise 제거를 위해서 삽입된 source follower의 pixel간 threshold voltage uniformity에 따라 noise가 발생할 소지가 증가하게 된다.

Toshiba 및 VLSI Vision 등 여러회사에서 사용하고 있는 구조이기도 하다.

3-Tr 구조의 동작원리는 다음과 같다.

step 1. Reset Tr이 ON 되면서 reset Tr의 source node potential이 VDD가 된다. 이렇게 하므로써 initialization이

끝나며 이때 reference value를 detection하게 된다.

step 2. 외부에서 수광부인 photo-diode에 빛이 입사 하게 되면 이에 비례하게 EHP가 생성된다.

step 3. 생성된 신호전하에 의하여 reset Tr의 source node(또는 select Tr의 gate bias node)의 potential 이

생성된 신호전하의 양에 비례하게 변화한다.

step 4. Select Tr의 gate bias가 신호전하량에 따라 변하게 되면 결과적으로 select Tr의 source node

(access Tr의 drain node)의 potential이 변하게 된다.

step 5. 이때 access Tr이 ON state가 되면 column 쪽으로 data가 readout 되게 된다.

step 6. Reset Tr이 ON 되면서 reset Tr의 source node potential이 VDD가 된다.

step 7. step 1. ~ step 6.이 반복된다.

4-Tr Structure

Readout noise 억제를 위해 1980년대에 일본의 Hamamatsu가 제안한 구조이다. CCD의 출력단과 거의 흡사한 구조를 가지고 있으며, 4개의 Tr과 1개의 photo-diode로 구성이 되어 있다. 이 구조의 경우 CCD와 마찬가지로 출력단을 floating diffusion node를 이용하므로 image lagging이 발생할 소지가 높다. 또한 3-Tr 구조와 마찬가지로 pixel내에 존재하는 Tr들의 threshold voltage uniformity에 따라 noise가 발생할 소지가 높으며, 1pixel당 Tr수가 상대적으로 다른 구조에 비해 많기 때문에 fill factor가 낮은 단점이 있다.

기존의 4-Tr 구조가 가지고 있는 image lagging문제를 해결하기 위하여 1993년에 JPL에서는 photo-gate type CMOS active pixel sensor(APS)를 제안하였다. 4-Tr photo-gate type CMOS APS의 경우, photo-diode 상단부에 photo-gate라는 전극을 올려 축적된 signal을 output floating node로 transfer가 잘 되도록 도움을 주기 위한 구조이다. 그러나 photo-diode 상에 존재하는 photo-gate를 poly 전극을 이용할 경우 제조된 소자의 광응답 특성이 나빠지는 단점(특히 blue response)이 있으며 이를 극복하기 위해서 transparent한 전극(Indium Tin Oxide : ITO)을 사용하기도 한다.

이러한 CMOS Image Sensor의 가장 큰 단점은 dark current가 크다는 것인데 이를 극복하기 위해서 CCD에서 적용하는 HAD(Hole Accumulated Device) 또는 PPD(Pinned Photo-Diode) 구조를 적용한다.

4-Tr photo-gate type CMOS APS의 동작원리는 다음과 같다.

step 1. Reset Tr이 ON 되면서 output floating diffusion node potential이 VDD가 된다. 이때 reference value를

detection하게 된다.

step 2. 외부에서 수광부인 photo-diode에 빛이 입사하게 되면 이에 비례하게 EHP가 생성된다.

step 3. 생성된 신호전하에 의하여 Transfer Tr의 source node의 potential이 생성된 신호전하의 양에 비례하게

변화한다.

step 4. Transfer Tr이 ON이 되면 축적된 신호전하는 floating diffusion node로 전달되게 되며 전달된 신호

전하량에 비례하게 output floating diffusion node의 potential이 변하며 동시에 select TR의 gate bias가

변화하게 된다. 이는 결국 select Tr의 source potential의 변화를 초래하게 된다.

step 5. 이때 access Tr이 ON state가 되면 column 쪽으로 data가 readout 되게

된다.

step 6. Reset Tr이 ON 되면서 output floating diffusion node potential이 VDD가 된다. 이러한 과정이 반복된다.

Photo-gate type 4-Tr 구조의 경우는 다음과 같다.

아래는 일반적인 흑백 CCD camera module의 구성을 나타낸다.

흑백 CCD의 경우, 일반적으로 4-chip solution으로 제공되며 color CCD의 경우는 아래 그림에서 보는 바와 같이 6-chip solution으로 제공되고 있다.

CMOS Image Sensor는 위의 그림에서 vertical driver, Timing generator, CDS/AGC/ADC, MICOM 및 EEPROM, Digital signal processor등을 one-chip화 시킬 수 있다.

현재 전세계 기술력은 digital signal processor를 동시에 one chip화 할 경우 발생하는 문제점을 확실히 제거를 하지 못하고 있는 실정이므로 일반적인 CMOS Image Sensor의 chip solution 은 2-chip solution으로 제공되고 있다.

Correlated Double Sampling(CDS) 기술

Correlated Double Sampling(CDS)이란 pixel에서 readout시 발생하는 noise를 제거하기 위하여 reference value와 signal value를 각각 읽어 두 값의 차이로부터 순수한 신호레벨을 찾아내는 방법을 말한다. VLSI Vision사에서 사용한 CDS를 살펴보면 아래의 그림과 같다.

CMOS Image Sensor glossary

Correlated Double Sampling(CDS)

Low frequency NOISE 제거를 위한 신호추출 방법.Pixel에서 신호를 Sampling 할 때, Reset & Integrating시 신호를 각각 읽어 들여 Reset noise와 DC Offset을 빼주기 위함이다.

Dark Current

[pA/cm2] or [nA/cm2] Definition ; Idark = (Signal Charge / Integration time)← Q = i×t , typically under the 1nA/cm2. c.f. : Dark Level , ( Q = CV )

Dynamic Range : [dB]

Definition ; = 20 log [Saturation Signal / Dark Signal (rms Noise floor)] , typically 60 ~ 70 dB.

Fill Factor (Aperture Efficiency) : [%]

Definition ; = Light Sensitive Area / 1 pixel Area ) X 100

Fixel Pattern Noise (FPN) :

전하 transfer circuit과 source follower circuit을 구성하는 Tr의 threshold mismatch 에 의해 주로 발생함. 이는 dark 상태에서 system gain을 높이면 눈으로 식별 가능하다. Gain type FPN 은 pixel size 가 작을때 pixel의 geometry 변화에 의해 발생한다.

Reset Noise (kTC Noise) :

개별 pixel 로부터 신호를 Readout 한 후, Reset 할 때 발생하는 thermal noise. k : Boltzmann constant , T : Kelvin, C : Junction Capacitance.

Quantum Efficiency : [%]

Definition = (Photo - generated electrons / Incident photons on the pixel Area) X 100 일반적으로 양자효율(quantum efficiency)라 함은 입사된 photon 1개당 생성되는 EHP의 개수를 의미한다.

참고 : https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=ngic315&logNo=20013751516

CMOS IMAGE SENSOR(CIS)

이미지 센서는 wafer 공정회사 또는 반도체 회사 에서 제조된다. 여기에 있는 조그만한 회로와 장치들은 실...

blog.naver.com

'[카메라·영상]' 카테고리의 다른 글

| 오버랩(Overlap) 기능이란.. (1) | 2022.08.26 |

|---|---|

| CMOS 이미지 센서의 메타비전: The Eye Beyond the Eye (0) | 2022.06.02 |

| mulit-ROI, Binning, dynamic range, image memory 등 example (0) | 2021.12.20 |

| Photo Engineering 기본 : 비전 시스템, 카메라, 조명, 광학 (0) | 2021.12.10 |

| 렌즈 사양서에서 F 값 ? (0) | 2021.12.10 |