메타 스테빌리티의 이해

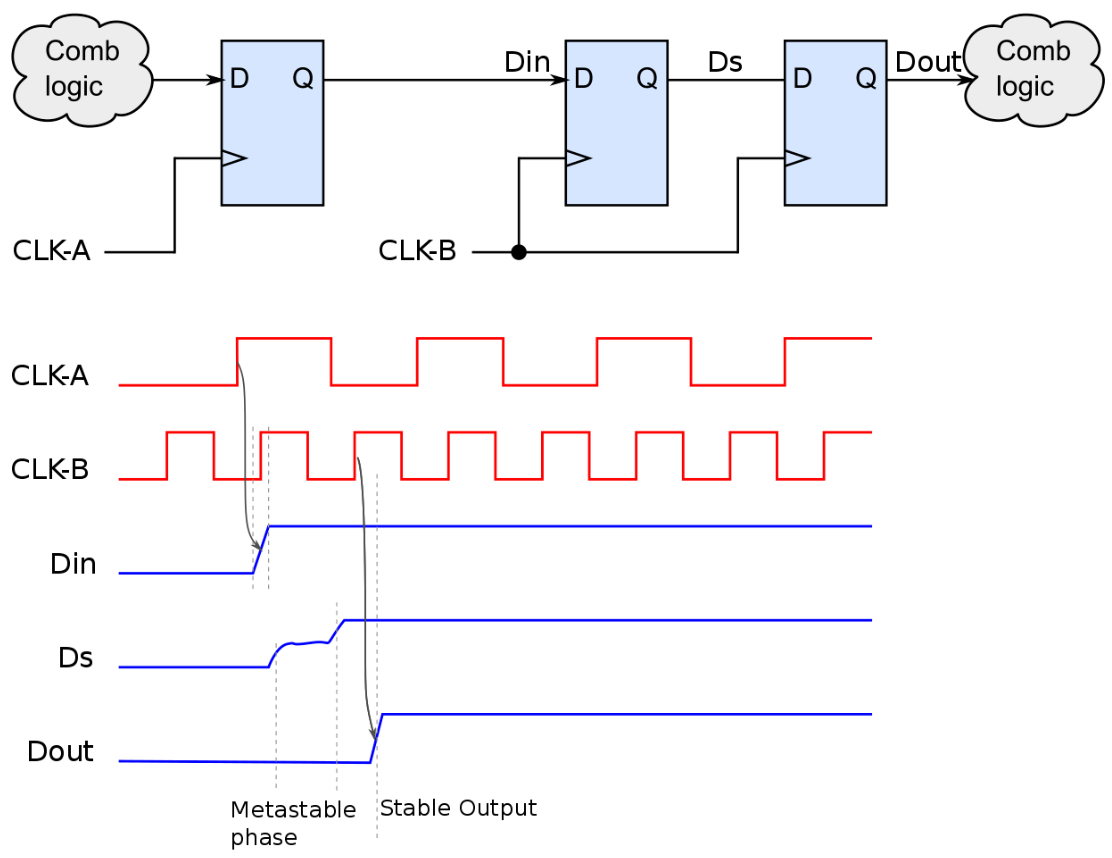

메타 스타 빌리티(MetaStability)는 신호가 관련이 없거나 async. clock domain의 회로간에 전송 될 때 FPGA를 포함한 digital device에서 시스템 장애를 일으킬 수있는 현상입니다.

이 백서에서는 FPGA의 metastability에 대해 설명하고 현상이 발생하는 이유를 설명하고 설계 실패를 일으킬 수있는 방법에 대해 설명합니다.

Metastability으로 인해 계산 된 MTBF (mean time between failures)는 설계자가 이러한 실패 가능성을 줄이기위한 조치를 취해야하는지 여부를 나타냅니다.

본 백서에서는 다양한 design 및 device parameter에서 MTBF를 계산하는 방법과 FPGA 벤더 및 설계자가 MTBF를 증가시킬 수있는 방법을 설명합니다.

설계 기법과 최적화를 통해 Metastability 실패 가능성을 줄임으로써 시스템 신뢰성을 향상시킬 수 있습니다.

![]() Understanding Metastability in FPGA - white Paper.pdf

Understanding Metastability in FPGA - white Paper.pdf

참조 : http://www.pldworld.com/_altera/html/tip/wp-01082-quartus-ii-metastability.pdf

'[FPGA]' 카테고리의 다른 글

| Intel FPGA (altera) Introduction to FPGA HIGH SPEED IO (0) | 2020.07.02 |

|---|---|

| [FPGA] pre-emphasis 란.. (0) | 2020.05.29 |

| altera의 LVDS SERDES block (DPA, Synchronizer, BitSlip) 분석 (0) | 2019.12.31 |

| BitSlip에 대한 이해 (understanding BITSLIP) (0) | 2019.12.31 |

| Metastability(메타스테빌리티)란? (0) | 2019.07.08 |