1. SPI(Serial Peripheral Interconnect) 버스란 |

SPI (Serial Peripheral Interconnect) 버스는 Motorola에 의해 개발된 전이중 (full duplex) 통신이 가능한 동기 통신 규격이다. I2C와 마찬가지로 마스터-슬레이브 방식으로 동작하며 마스터가 동기를 위한 클럭을 출력한다. 각 SPI 슬레이브 장치는 chip enable (/CE) 입력을 가지고 있으며 이 입력이 활성화되었을 때에만 동작한다. 따라서 마스터는 여러 개의 slave select (SS) 선을 슬레이브들의 /CE에 연결하고 한 순간에 하나의 슬레이브만 선택하는 방법을 사용하여 두 개 이상의 슬레이브 장치들을 구동할 수 있다. SPI의 통신 속도는 최고 70 MHz에 이르기 때문에 I2C에 비해 훨씬 빠르다.

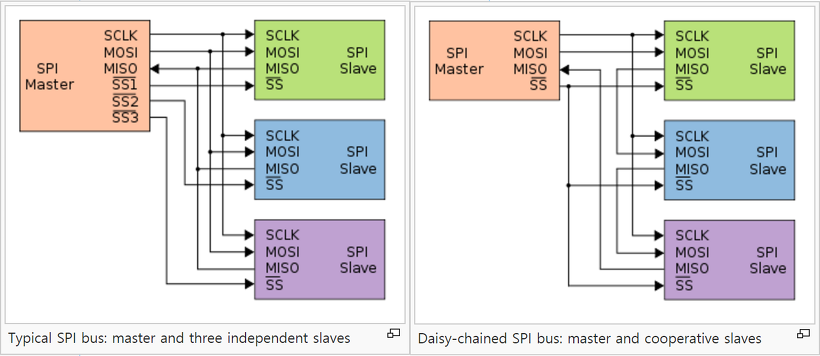

다음 그림은 SPI 버스를 통해 마스터에 복수의 슬레이브가 연결된 상황을 보여준다.

그림에 표시된 4 개의 신호는 SPI 버스에서 정의된 신호이다.

● SCLK : Serial Clock. 마스터가 출력하는 동기용 클럭

● MOSI : Master Output Slave Input. 마스터의 출력이며 슬레이브에게는 입력

● MISO : Master Input Slave Output. 슬레이브의 출력이며 마스터에게는 입력

● SS : Slave Select. 매스터의 출력으로 슬레이브를 선택하기 위한 신호, 입력이 ‘0’인 동안에만 활성화

2. SPI 통신 방식 |

통신을 진행하기 위해서 마스터는 우선 SS로 ‘0’을 출력하여 해당 슬레이브를 활성화시킨다. 그런 다음 마스터는 SLCK로 동기를 위한 클럭을 출력하는데 이 클럭에 맞추어 MOSI로 데이터를 한 비트씩 내보낸다. 이와 동시에 마스터는 자신이 출력하는 클럭에 맞추어 MISO를 한 비트씩 읽는다. 다시 말해서 SPI 마스터는 자신의 출력인 SCLK에 맞추어 MOSI로 데이터를 내보내며 동시에 MISO로는 데이터를 수신한다. SPI 버스는 언제나 양방향 통신을 진행한다. SCLK에 맞추어 MOSI로 데이터를 출력하는 동안 MISO로는 데이터가 수신된다. 수신되는 데이터는 상황에 따라 의미가 있는 값일 수도 있고 쓰레기 값일 수도 있다. 마찬가지로 슬레이브의 데이터를 읽기 위하여 SLCK에 맞추어 MISO로 입력을 받는 동안 MOSI로는 데이터가 출력된다.

보통 SPI 통신은 8 비트 단위로 진행되지만 12 비트나 16 비트 또는 그 이상의 길이가 한 단위가 될 수도 있다. 비트 전송 순서에 대한 규정은 없다. 데이터의 전송은 MSB부터 시작될 수도 있고 LSB부터 시작될 수도 있다. 데이터를 연속 전송하는 경우 한 단위의 데이터를 보낼 때마다 SS 신호를 매번 인가할 수도 있지만 SS 신호를 ‘0’으로 설정한 후 모든 데이터를 다 보낼 때까지 이 상태를 유지하고 있다가 데이터의 전송이 끝났을 때 SS를 ‘1’로 바꿀 수도 있다. SPI 규격은 이런 부분까지 규정하고 있지 않으며 마스터와 슬레이브 사이의 약속에 따라 결정된다. SPI 슬레이브 장치의 용도와 특성에 따라 사용 방법이 다르므로 슬레이브 장치의 데이터쉬트를 반드시 확인해야 한다.

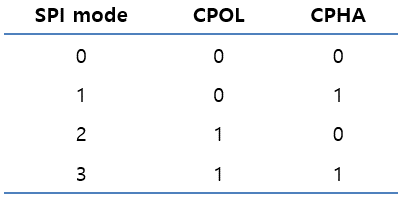

3. SPI 모드(mode) |

SPI 매스터와 슬레이브는 매스터의 출력인 SCLK에 맞추어 데이터를 한 비트씩 교환한다. 그런데 클럭에 동기를 맞추는 방법은 한 가지만 있는 것이 아니다. 클럭이 출력되고 있지 않은 상황에서 클럭의 기본 값은 ‘0’일 수도 있고 ‘1’일 수도 있다. 그리고 매스터와 슬레이브가 매 클럭의 라이징 에지에서 데이터를 읽을 수도 있고 매 클럭의 폴링 에지에서 데이터를 읽을 수도 있다. 앞의 특성을 클럭의 극성 (polarity)이라고 하고 뒤의 특성을 클럭의 위상 (phase)이라고 한다. 클럭의 극성과 위상의 조합에 따라 모두 4 가지 방법이 사용 가능하다. SPI 슬레이브는 4 가지 가능한 방법 중 한 가지를 사용하도록 만들어지고 매스터는 4 가지 방법을 모두 지원해야 한다.

위의 4 가지 극성과 위상 조합에 0에서 3까지의 숫자를 부여하여 이를 SPI 모드라고 부른다.

4. 두 개 이상의 SPI 슬레이브 연결 |

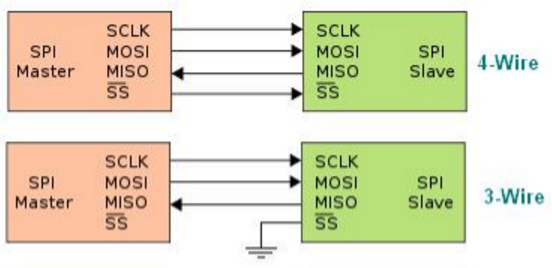

I2C 버스처럼 SPI 버스에서도 한 개의 마스터가 두 개 이상의 슬레이브와 연결될 수 있다. I2C 슬레이브가 고유한 주소를 가지고 있는 것처럼 각각의 SPI 슬레이브는 chip enable (/CE) 신호를 가지고 있다. SPI 마스터는 각 슬레이브의 /CE 신호를 제어하여 원하는 슬레이브를 선택한다. 다음 그림은 한 개의 SPI 마스터에 두 개의 슬레이브들을 연결하는 방법을 설명한다.

세 장치의 SCLK, MOSI, MISO는 각각 서로 연결되어 있지만 슬레이브의 /CE 신호들은 서로 묶이지 않고 마스터의 다른 핀들로 연결된다. 슬레이브의 수에 상관없이 한 순간에는 하나의 슬레이브만 마스터와 통신할 수 있다. 두 슬레이브가 모두 활성화되면 슬레이브의 출력인 MISO에서 데이터의 충돌이 일어난다. 그래서 마스터는 자신이 원하는 슬레이브의 /CE 신호만 ‘0’으로 설정하여 활성화시키고 나머지 슬레이브의 /CE는 ‘1’로 두어야 한다. /CE 입력이 ‘1’인 슬레이브는 선택되지 않았기 때문에 자신의 MISO 출력을 hi-Z 상태로 만들어 선택된 슬레이브와 마스터 간의 통신에 영향을 주지 않는다. 따라서 모든 SPI 슬레이브의 MISO 출력은 3 상태를 지원한다. /CE 입력이 ‘1’인 슬레이브는 당연히 마스터가 출력한 SCLK와 MOSI 신호를 무시한다.

세 개 이상의 슬레이브도 같은 방법으로 마스터와 연결할 수 있다. 슬레이브의 수가 하나씩 늘어날 때마다 새로운 슬레이브를 위한 /CE 신호만 하나 더 필요할 뿐이다. 그런데 이 때 마스터에 연결된 슬레이브들이 사용하는 SPI 모드가 한 가지가 아니거나 비트 전송 순서가 다를 수 있는데 이런 경우에는 통신의 효율이 많이 낮아진다. 가령 어떤 슬레이브는 모드 0을 사용하고 또 다른 슬레이브는 모드 1을 사용한다면 마스터가 슬레이브를 바꿀 때마다 동작 모드를 매번 다시 설정해야 한다. 또한 동작 모드가 같아도 비트 전송 순서가 다르다면 마찬가지 문제가 생긴다.

마스터가 하나의 슬레이브만 구동한다면 슬레이브의 /CE 신호를 GND로 고정시켜 두어도 상관없다. 어차피 SCLK, MOSI, MISO를 공유할 다른 슬레이브가 없기 때문에 이 선들은 하나뿐인 슬레이브 전용으로 사용된다. 그렇기 때문에 슬레이브를 항상 활성화시켜 둬도 기능상의 문제는 생기지는 않는다.

5. SPI 통신의 예 |

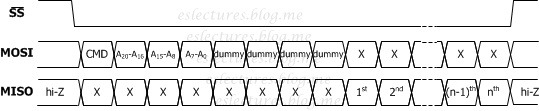

AT45DB161D은 SPI 인터페이스를 사용하는 16 Mbit 직렬 플래쉬 메모리이다. 이 플래쉬 메모리에 정보를 기록하거나 저장된 정보를 읽기 위한 여러 방법 중 다음 그림은 main memory page read 명령을 설명하고 있다. 이 그림에서 데이터는 바이트 단위로 표시되어 있다.

main memory page read 명령은 AT45DB161D 내부의 특정 페이지의 내용을 연속으로 읽기 위한 것이다. 이 플래쉬 메모리의 용량은 2 Mbytes이므로 주소를 지정하기 위해서 21 비트가 필요하다. 마스터는 가장 먼저 AT45DB161D의 /CE 신호를 ‘0’으로 만든 다음 main memory page read를 위한 8 비트 명령을 출력하고 이어서 읽기를 원하는 주소 3 바이트를 출력한다. (AT45DB161D는 MSB 우선의 비트 전송 순서를 사용한다.) main memory page read 명령과 3 바이트 주소를 받으면 AT45DB161D는 저장된 데이터를 읽어서 출력할 준비를 하는데 이 과정에 시간이 필요하다. 이를 위해 마스터는 4 바이트를 더 출력한다. 마스터가 추가로 전송하는 4 바이트를 전송하는 것은 SLCK를 출력하기 위한 동작이므로 출력하는 데이터는 어떤 값이든 상관없다.

이렇게 8 바이트를 MOSI로 출력하는 동안 계속해서 마스터의 MISO로 AT45DB161D의 출력이 들어오지만 이 값은 아무런 의미가 없는 쓰레기 값이다. AT45DB161D의 데이터 전송은 9 번째 바이트부터 시작된다. AT45DB161D는 9 번째 바이트에서 마스터가 지정한 주소의 내용을 MISO로 출력한 후 내부 카운터를 사용하여 주소를 1 증가시킨다. 이 후 마스터가 MOSI로 한 바이트씩 출력할 때마다 AT45DB161D는 데이터를 출력하고 주소를 1 증가시키는 과정을 계속 되풀이한다. 이런 과정을 통해 마스터는 AT45DB161D의 데이터를 필요한 만큼 연속해서 읽고 마지막으로 AT45DB161D의 /CE 신호를 ‘1’로 만들어 통신을 끝낸다. 9 번째 바이트부터 마스터가 SCLK를 출력할 뿐 MOSI로 출력해야 하는 데이터는 없으므로 어떤 값을 보내도 상관 없다.

이 명령 외에도 AT45DB161D을 사용에 필요한 다른 많은 명령들이 더 있다. 각 명령마다 위 그림과 비슷한 타이밍도를 가지고 있으므로 각 명령의 쓰임새와 사용법을 알려면 AT45DB161D의 데이터쉬트를 참고해야 한다.

6. 관련문서 및 출처 |

출처: https://twinw.tistory.com/149 [흰고래의꿈]

'[통신]' 카테고리의 다른 글

| AXI bus signal 각각에 대한 설명 (0) | 2021.04.29 |

|---|---|

| CTLE, DFE란? (0) | 2021.01.26 |

| UART(범용 비동기화 송수신기: Universal asynchronous receiver/transmitter) (0) | 2019.08.23 |

| 네트워크 부팅에 관한 소개 (0) | 2018.08.09 |

| 광전송 네트워크의 이해 (0) | 2018.05.11 |